Master les verrous SR: symboles, fonctions et applications pratiques

Un verrou SR est un circuit asynchrone qui fonctionne indépendamment des signaux d'horloge, ce qui en fait un outil polyvalent dans diverses applications.Il maintient un état binaire - élevé (1) ou bas (0) - et peut stocker un seul morceau d'informations, qu'il détient jusqu'à ce que les nouveaux signaux d'entrée dictent un changement.Cet élément de stockage binaire de base est construit à l'aide de deux portes logiques à couplage croisée, généralement ni des portes NAND.Le (s) entrée (s) set active le verrou, réglant la sortie (Q) à haut, tandis que l'entrée de réinitialisation (R) définit la sortie à faible.Cependant, des signaux élevés simultanés sur les deux entrées conduisent à un état non défini, une condition que les concepteurs doivent éviter.Les verrous SR ne sont pas seulement des constructions théoriques;Ils sont mis en œuvre dans des systèmes pratiques pour conserver des données temporaires, prendre en charge les résultats du traitement intermédiaire et même gérer la détection des erreurs dans des applications critiques telles que les dispositifs aérospatiaux et médicaux, présentant leur indispensabilité dans la conception des circuits numériques.Catalogue

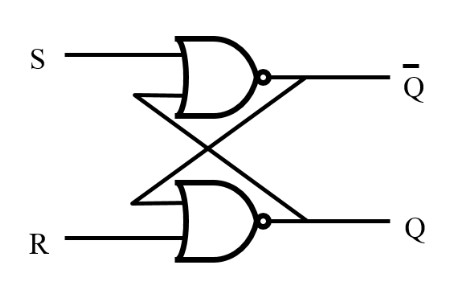

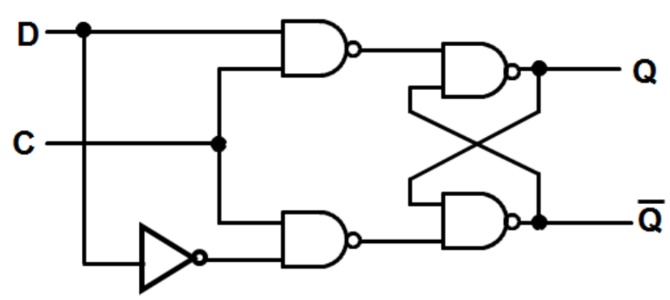

Figure 1: Latch SR

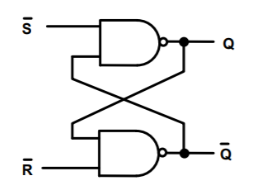

Qu'est-ce qu'un verrou SR?

Un verrou SR, ou verrouillage de réinitialisation, est un élément de stockage binaire de base qui appartient à la catégorie des circuits asynchrones.Contrairement aux circuits synchrones, les verrous SR fonctionnent sans signal d'horloge, en s'appuyant uniquement sur le contrôle direct des signaux d'entrée.Cela leur permet de fonctionner indépendamment dans les circuits numériques.Un verrou SR peut maintenir deux états stables: élevé (1) et bas (0), ce qui lui permet de stocker un seul peu d'informations jusqu'à ce qu'ils soient mis à jour par de nouveaux signaux d'entrée.

La construction d'un verrou SR implique généralement deux portes logiques couplées à couplage, généralement ni des portes ou des portes NAND.Dans une conception de verrouillage SR en utilisant Nor Gates, la sortie de chaque porte est connectée à l'entrée de l'autre, formant une boucle de rétroaction.Cette configuration garantit que le verrou peut changer rapidement les états en fonction des signaux d'entrée tout en maintenant la stabilité jusqu'à ce qu'une nouvelle entrée incite un changement.

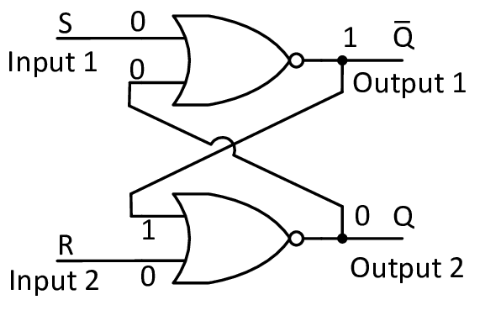

Figure 2: Latch SR (2)

Entrée (s) de définition: lorsque les entrées définies sont activées (haut), la sortie du verrou (Q) passe à High (1).

Entrée de réinitialisation (R): Lorsque l'entrée de réinitialisation (R) est activée (élevée), la sortie (Q) passe à Low (0).

Les deux entrées élevées: si les entrées S et R sont élevées simultanément, le verrou est dans un état non défini, qui doit être évité dans la conception.

Les verrous SR sont essentiels pour le stockage temporaire des données et les résultats intermédiaires maintenus dans les systèmes numériques.Ce sont les éléments fondamentaux dans des circuits séquentiels plus complexes comme les registres de décalage multi-bits, les unités de mémoire et certains types de compteurs.

Dans ces applications, les verrous SR fournissent une rétention stable des données et peuvent rapidement répondre aux modifications des signaux externes, assurant le fonctionnement efficace de l'ensemble du système électronique.

Une autre application critique des verrous SR est en cas de détection d'erreur et de logique de correction dans les circuits numériques.En raison de leur capacité à tenir un état stable, ils peuvent surveiller les changements d'état du système et revenir rapidement à un état sûr prédéfini lors de la détection d'une anomalie.Cette fonctionnalité est particulièrement précieuse dans les systèmes à haute fiabilité tels que l'aérospatiale et les dispositifs médicaux.

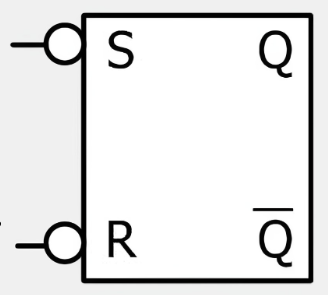

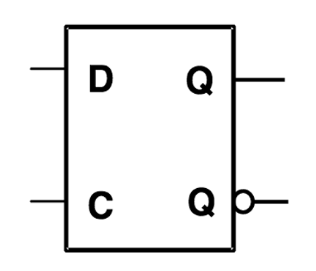

Symbole du verrou SR

Comprendre son symbole et sa structure est fondamental pour saisir son fonctionnement et son utilisation pratique.Dans les diagrammes de circuits, le verrou SR a généralement deux ports d'entrée principaux étiquetés S (SET) et R (réinitialisation).Ces entrées contrôlent l'état de sortie du verrouillage, généralement représenté comme Q. Certaines conceptions comportent également la sortie inverse, étiquetée Q ', qui fournit l'état opposé de Q.

Figure 3: Symbole du verrou SR

Un verrou SR est souvent représenté par un symbole rectangulaire avec les entrées S et R et une sortie Q. Dans certains cas, la sortie Q 'est également affichée.Cet étiquetage clair permet aux concepteurs de circuits d'identifier rapidement la fonction du composant et son rôle dans le plus grand circuit.

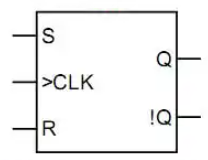

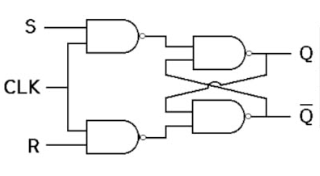

Une variante commune du verrou SR comprend une entrée d'horloge (CLK).L'entrée CLK garantit que les changements d'état se produisent en synchronisation avec le signal d'horloge, permettant un contrôle de synchronisation précis.Dans cette configuration, même si S ou R sont activés, l'état du verrouillage ne se met à jour que lorsque le signal CLK remplit des conditions spécifiques, généralement sur le bord montant ou descendant.Cela empêche les erreurs causées par des problèmes de signal d'entrée ou des changements involontaires.

Figure 4: Symbole du verrou SR de l'horloge

Le symbole de verrouillage SR chronométré comprend les entrées S, R et CLK à l'intérieur d'un rectangle.Cette représentation standardisée aide les concepteurs à comprendre la fonctionnalité du verrou et ses exigences de synchronisation.Par exemple, dans le calcul haute performance ou les systèmes de transfert de données complexes, un contrôle CLK minutieux garantit que les données sont stockées et transférées avec précision à chaque étape de traitement, optimisant les performances et la fiabilité globales du système.

Un contrôle précis des entrées de verrouillage SR est important, en particulier dans la conception de la mémoire à grande vitesse et de grande capacité ou des tampons de données temporaires.En concevant des circuits logiques pour gérer l'activation S et R, des fonctions complexes telles que le chargement des données, la compensation ou la réinitialisation d'état peuvent être obtenues.Le contrôle précis du signal CLK garantit que toutes les opérations de données suivent une séquence de synchronisation prédéfinie, améliorant considérablement l'efficacité du système et la capacité de traitement des données.

Une compréhension approfondie du symbole et de la structure du verrou SR non seulement dans la conception et le dépannage des circuits corrects, mais aussi dans l'exécution des opérations de logique numérique complexes et l'amélioration des performances du système.Ceci est particulièrement essentiel dans les applications nécessitant une forte fiabilité et un contrôle précis, tels que l'aérospatiale et les dispositifs médicaux.

Types de loquets et leurs principes de travail

Les verrous sont des composants fondamentaux de la conception électronique, offrant des fonctions diverses et des applications larges.Les principaux types de verrous sont les verrous SR et les verrous D, chacun avec des opérations uniques et des cas d'utilisation.

Loquet SR

Le verrou SR, ou verrou de réinitialisation set, est un périphérique de stockage de base contrôlé par ses deux entrées, S (SET) et R (réinitialisation).

Lorsque l'entrée S reçoit un signal élevé, la sortie Q devient élevée, indiquant que les données sont définies.Lorsque l'entrée R reçoit un signal élevé, la sortie Q devient faible, indiquant que les données sont réinitialisées.Si les entrées S et R sont élevées simultanément, le verrou est dans un état non défini, provoquant une instabilité potentielle de sortie.Cette condition doit être évitée dans la conception.La réponse directe du verrouillage SR aux signaux d'entrée le rend utile dans des situations nécessitant une réaction rapide.

Verrure

Le verrou D, également connu sous le nom d'un verrou de données ou de verrouillage transparent, offre un contrôle plus complexe avec l'entrée de données D et le signal d'horloge CLK.

Figure 5: D Latch

Figure 6: S symbole de verrouillage

Lorsque CLK est élevé, la sortie Q suit l'entrée D, permettant aux données de passer librement le verrou.Lorsque CLK est faible, la valeur de courant de D est verrouillée et la sortie q reste constante jusqu'au prochain signal CLK élevé.Ce mécanisme rend le verrou D Idéal pour stocker temporairement des données pour synchroniser différentes vitesses de traitement dans un système.

Les verrous SR et D ont un rôle inégalé dans le stockage des données et la logique de la machine d'état.En raison de leur réponse directe au niveau d'entrée, les verrous sont essentiels dans la conception de circuits asynchrones.Ils fournissent des fonctions vitales pour les transferts de données complexes et les systèmes de gestion de l'énergie, stockant efficacement les informations d'état pour assurer un fonctionnement stable.Une utilisation appropriée de ces loquets peut améliorer considérablement la fiabilité et l'efficacité des circuits, ce qui les rend indispensables dans les systèmes électroniques modernes.

Tableau de vérité d'un verrou SR

Figure 7: Latch Sr Nand

|

S |

R |

Q |

Q ' |

Note |

|

0 |

0 |

1 |

1 |

INTERDIT |

|

0 |

1 |

1 |

0 |

ENSEMBLE |

|

1 |

0 |

0 |

1 |

RÉINITIALISER |

|

1 |

1 |

Q |

Q ' |

RETENIR |

Graphique 1: Tableau de vérité de Sr Latch en utilisant NAND Gates

Figure 8: SR ni verrouillage

|

S |

R |

Q |

Q ' |

Note |

|

0 |

0 |

Q |

Q ' |

RETENIR |

|

0 |

1 |

1 |

0 |

RÉINITIALISER |

|

1 |

0 |

0 |

1 |

ENSEMBLE |

|

1 |

1 |

0 |

0 |

INTERDIT |

Graphique 2: Tableau de vérité du verrou SR en utilisant ni portes

Maintenant, nous prenons la table de vérité du verrou SR en utilisant Nor Gate comme exemple pour comprendre la signification de la table de vérité du verrou SR.

États d'entrée et de sortie

S et R sont 0: le verrou reste dans son état actuel.La sortie Q reste la même, qu'elle soit 0 ou 1.

S est 0 et R est 1: le verrou réinitialise, forçant la sortie Q à 0.

S est 1 et R est 0: les ensembles de verrouillage, ce qui rend la sortie Q égale à 1.

S et R sont 1: cette condition n'est pas valide ou non définie, souvent appelée l'état "interdit" dans un verrou SR.Dans ce cas, Q et Q 'égaux 0, conduisant à une sortie ambiguë.

Lorsque S et R sont tous deux 0, le verrou ne fait rien et détient simplement sa valeur actuelle.Ceci est utile pour maintenir l'état sans modifications.

Lorsque S est 0 et R est 1, le verrou est explicitement dit de réinitialiser, s'assurant que Q est 0 quel que soit son état précédent.C'est un moyen simple de nettoyer le verrou.

Lorsque S est 1 et R est 0, le verrou est réglé, assurant que Q devient 1. C'est ainsi que vous stockez un «1» dans le verrou.

Lorsque S et R sont tous deux 1, l'état n'est pas autorisé car il fait que les deux sorties sont 0, ce qui est contradictoire et peu fiable.Les concepteurs doivent éviter cette condition pour assurer un fonctionnement stable.

Avantages et inconvénients des verrous

Les verrous sont largement utilisés dans la conception de circuits numériques en raison de leur simplicité et de leur faible coût.Ces caractéristiques permettent aux verrous de fonctionner à grande vitesse avec une faible consommation d'énergie, ce qui les rend idéales pour les systèmes numériques à grande vitesse.Par exemple, dans les fichiers de registre du processeur, les verrous peuvent rapidement stocker et récupérer des données, augmentant considérablement la vitesse de traitement et l'efficacité.

Avantages des verrous

Simplicité et rentabilité: les verrous sont des composants simples qui sont peu coûteux à mettre en œuvre dans les circuits numériques.

Haute vitesse et faible puissance: leur conception permet un fonctionnement rapide avec une consommation d'énergie minimale, ce qui est essentiel dans les systèmes numériques à grande vitesse.

Efficacité de la gestion des données: dans des applications telles que les fichiers de registre de processeurs, les verrous fournissent un stockage et une récupération de données rapides, améliorant les performances globales du système.

Inconvénients des verrous

Malgré leurs avantages, les verrous ont des limites notables dans certaines conceptions et applications.

Comportement imprévisible dans les conceptions asynchrones: sans contrôle du signal d'horloge, les verrous peuvent se comporter de manière imprévisible.Dans les verrous SR, si les entrées définies et réinitialisées (R) sont élevées simultanément, la sortie devient non définie, conduisant à l'instabilité.Ceci est problématique dans les applications de contrôle ou de sécurité en temps réel, où une sortie fiable est cruciale.

Conception de synchronisation complexe: la conception avec des verrous nécessite des considérations de synchronisation minutieuses.Les ingénieurs doivent tenir compte des retards de propagation du signal et des conditions de course pour éviter les erreurs de synchronisation.Une mauvaise conception peut entraîner des changements de données avant que le signal d'horloge ne se stabilise, provoquant une corruption des données ou une capture de données incorrecte.Cela nécessite une compréhension approfondie de l'analyse du synchronisation et du comportement du circuit.

Pour relever ces défis, des techniques et des stratégies de conception spécifiques peuvent être utilisées:

Mécanismes de synchronisation: l'ajout de mécanismes de synchronisation peut aider à gérer les entrées asynchrones et à atténuer les comportements imprévisibles.

Gestion de l'horloge personnalisée: la mise en œuvre de stratégies de gestion d'horloge personnalisées peut garantir que les données sont correctement verrouillées et au bon moment.

Utilisation des outils EDA: les outils d'automatisation de la conception électronique moderne (EDA) offrent des capacités avancées d'analyse et d'optimisation.Ces outils aident à prédire et à résoudre les problèmes de synchronisation et de synchronisation pendant la phase de conception, en améliorant la fiabilité et les performances des systèmes numériques à l'aide de verrous.Ils aident les concepteurs à identifier les problèmes potentiels tôt, garantissant que le produit final fonctionne de manière fiable dans diverses conditions.

Applications pratiques des verrous SR

Les verrous SR, connus pour leur capacité à maintenir rapidement et de manière fiable, sont largement utilisés dans divers systèmes électroniques.Ils excellent dans des scénarios nécessitant un stockage temporaire de données ou une rétention d'état.

Stockage de données temporaire

Les verrous SR sont souvent utilisés dans la mémoire du cache pour stocker temporairement les données.Cela permet au système d'accéder rapidement aux données fréquemment utilisées, augmentant considérablement les capacités de traitement des données et l'efficacité des processeurs à grande échelle.

Fichiers de registre de stockage

Dans les processeurs, les verrous SR permettent un stockage rapide et une récupération des données dans les fichiers d'enregistrement, améliorer la vitesse de traitement et les performances globales du système.

Maintenir des signaux de contrôle

Dans les systèmes de contrôle numérique, les verrous SR sont utiles pour maintenir l'état de certains signaux de contrôle jusqu'à ce que les conditions externes ou la logique système dicte un changement.En outre, ils aident à conserver les États au sein du système, garantissant des performances cohérentes dans les opérations qui nécessitent une précision et une fiabilité.

Circuits de déclenchement et de comptoir

Les bascules basées sur les verrous SR sont couramment utilisés dans les circuits nécessitant un fonctionnement synchronisé, tels que les horloges et les minuteries numériques.Ils contrôlent les impulsions du nombre, garantissant un chronomètre précis et des performances fiables.Ces circuits reposent sur les verrous SR pour maintenir des dénombrements précis, ce qui facilite la synchronisation et le séquençage dans les systèmes numériques.

Interactions mécaniques

Les verrous SR sont efficaces pour éliminer le rebond mécanique dans les commutateurs.Un rebond mécanique se produit lorsqu'un interrupteur génère des changements de signal rapides et répétitifs en raison d'un mauvais contact.Les verrous SR stabilisent le signal de sortie, empêchant les erreurs causées par des signaux bruyants.

Tong SR

Une bascule SR, souvent appelée bascule de set-réinitialisation déclenchée par le bord, se compose de deux verrous SR interconnectés.Cette structure à double retrait lui permet de répondre à des bords de signal d'horloge spécifiques (en hausse ou en descendant) pour modifier son état.Ceci est réalisé grâce à un contrôle logique spécial entre les verrous.La sortie du premier verrou devient une partie de l'entrée pour le deuxième verrou, et la sortie du deuxième verrou, à son tour, influence le premier verrou, créant une boucle de rétroaction imbriquée.

Figure 7: Talle SR

Le SR Flip-Flop change précisément au bord de la montée ou de la chute du signal de l'horloge.La rétroaction entre verrouillage entre les deux verrous SR garantit que la bascule ne change que l'état en réponse au bord de l'horloge, fournissant une sortie stable et fiable.

Dans les microprocesseurs et les processeurs de signaux numériques, les tongs SR sont utilisés pour l'échantillonnage et le stockage des données.Ils capturent et stabilisent les données sur des bords d'horloge spécifiés, garantissant un traitement et une analyse des données ultérieures fiables.

Le mécanisme de déclenchement des bords aide à éviter les conditions de course, où différentes parties du circuit peuvent changer l'état en même temps sans synchronisation, entraînant potentiellement des sorties instables ou incorrectes.Les bascules SR sont cruciales dans la mise en œuvre de la logique de protocole de communication spécifique, telles que la synchronisation du trame et la détection des erreurs.Leur stabilité et le temps de réponse rapide aident à maintenir la qualité de la transmission des données et la fiabilité du système.

États interdits dans les verrous SR et les tongs SR

Lors de la conception de verrous SR et de tongs SR à l'aide de NAND et Nor Gates, nous devons tous prêter attention à la gestion et à l'évitement des états inhibés.Un état interdit se produit lorsque les entrées d'ensemble et de réinitialisation (R) sont simultanément élevées (pour les portes NAND) ou faibles (pour ni les portes).Cette combinaison conduit à un état de sortie indéterminé, car la sortie dépend de l'état précédent du circuit, ce qui le rend imprévisible.

États interdits dans les verrous de Nand Gate SR

Lorsque S et R sont faibles, les deux sorties sont élevées, ce qui viole la caractéristique de sortie complémentaire du loquet.Il en résulte un état indéterminé.

États interdits dans Nor Gate Sr Latches

Lorsque S et R sont élevés, les deux sorties deviennent faibles, créant également un état indéterminé.Cela peut conduire à un comportement imprévisible dans le circuit.

Approches pratiques pour éviter les États interdits

Ajout de la logique de contrôle

Utilisez des portes logiques supplémentaires pour surveiller les états de S et R. Si les deux entrées se penchent vers un état interdit, ajustez automatiquement une entrée pour empêcher l'état indéterminé.Cela garantit que les sorties restent stables et prévisibles.Implémentez une porte logique qui intervient lorsque S et R sont à la fois élevés (ou bas), ajustant une entrée pour maintenir un état valide.

Simulation logicielle et tests de matériel

Effectuer des simulations logicielles approfondies pour identifier les états interdits potentiels dans diverses conditions de fonctionnement.Cela permet aux concepteurs de repérer et de corriger les erreurs logiques avant l'implémentation physique.Effectuez des tests matériels approfondis pour valider que le circuit gère correctement toutes les combinaisons d'entrée.Cette étape permet de garantir que le verrou ou la bascule fonctionne de manière fiable dans des scénarios du monde réel.

Conclusion

La polyvalence et la fiabilité des verrous SR soulignent leur signification dans la conception des circuits numériques.En explorant le comportement nuancé des verrous SR à travers leurs représentations de symboles, leurs tables de vérité et leurs applications pratiques, nous obtenons une compréhension complète de leur fonctionnement et de leur importance.Malgré les pièges potentiels des états non définis dans les conceptions asynchrones, la mise en œuvre stratégique de la logique de contrôle et de la simulation étendue peut atténuer ces risques.Les outils avancés de l'automatisation de la conception électronique (EDA) améliorent encore la fiabilité et les performances des circuits incorporant des verrous SR en prédisant et en résolvant les problèmes de synchronisation et de synchronisation.Qu'ils soient utilisés dans le stockage temporaire des données, la maintenance du signal de contrôle ou la détection d'erreurs, les verrous SR s'avèrent être fondamentaux pour créer des systèmes numériques robustes et efficaces.Leur rôle dans les opérations de mémoire à grande vitesse et le traitement des données synchrones dans des applications complexes illustre leur pertinence durable.À mesure que la technologie progresse, les principes régissant les verrous SR continuent d'informer et d'inspirer les innovations dans l'électronique numérique, garantissant que ces composants élémentaires restent intégrés au développement d'appareils électroniques sophistiqués et fiables.

Questions fréquemment posées [FAQ]

1. Qu'est-ce qu'un verrou SR?

Un verrou SR, ou verrouillage de réinitialisation, est un élément de stockage binaire fondamental utilisé dans les circuits numériques.Il s'agit d'un circuit asynchrone, ce qui signifie qu'il fonctionne sans signal d'horloge, en s'appuyant sur le contrôle direct de ses entrées pour changer les états.

2. Quelle est la fonction de SR dans la logique?

Dans la logique, les entrées SR (Set-Resset) contrôlent l'état du verrou.

3. Quel type de porte logique un verrou SR utilise-t-il?

Un verrou SR utilise généralement ni les portes ni les portes NAND.Dans un verrou SR basé sur NOR GATE, la sortie de chaque porte NOR est renvoyée dans l'entrée de l'autre, créant une boucle de rétroaction stable.Dans un verrou SR basé sur NAND Gate, une configuration de rétroaction similaire est utilisée, mais les niveaux de logique sont inversés par rapport au verrou bas basé sur NOR GATE.Les deux configurations obtiennent les mêmes fonctionnalités de base de la maintenance d'un état binaire basé sur l'ensemble et réinitialisent les entrées.

4. Comment fonctionne un verrou?

Un verrou fonctionne en utilisant la rétroaction pour maintenir son état de sortie en fonction des entrées fournies.Dans un verrou SR, les entrées de jeu et de réinitialisation (R) contrôlent l'état de la sortie (q).Lorsque l'entrée définie est activée (élevée), la sortie est réglée sur élevée (1).Lorsque l'entrée de réinitialisation est activée (élevée), la sortie est réinitialisée à faible (0).La boucle de rétroaction dans la conception du verrouillage garantit qu'une fois un état de sortie établi, il reste stable jusqu'à ce qu'un nouveau signal d'entrée le modifie.

5. Quel est le désavantage avec un verrou SR?

L'inconvénient principal d'un verrou SR est l'état non défini qui se produit lorsque les deux (s) entrées (s) et réinitialisation (R) sont élevées simultanément.Cette condition conduit à un état de sortie indéterminé, qui peut provoquer une instabilité et un comportement imprévisible dans les circuits numériques.Cet état "interdit" doit être évité dans la conception pour assurer un fonctionnement fiable.

Latch SR, verrouillage de réinitialisation, circuit asynchrone, élément de stockage binaire, circuits numériques, ni portes, portes NAND, boucle de rétroaction, état élevé, état bas, état indéfini, signal d'horloge, contrôle direct, stockage temporaire de données, tenue de résultat intermédiaire,Détection d'erreurs, applications aérospatiales, dispositifs médicaux, conception de circuits, verrouillage SR chronométré, signaux d'entrée, symbole et structure, mémoire à grande vitesse, tampons de données, contrôle de synchronisation, contrôle précis, rétention d'état, microprocesseurs, processeurs de signaux numériques, échantillonnage de données, donnéesStockage, déclenchement à bord, bascule SR, rétroaction entre verrouillage, conditions de course, logique du protocole de communication, synchronisation du cadre, détection d'erreurs, problèmes de signal, automatisation de conception électronique, outils EDA, mécanismes de synchronisation, gestion de l'horloge personnalisée, erreurs de synchronisation, retards de propagation,Conditions de course, transferts de données complexes, systèmes de gestion de l'alimentation, rebond mécanique, applications pratiques, systèmes de contrôle numérique, portes logiques, simulations logicielles, tests de matériel, états interdits, fiabilité du verrou.