Guide innovant des tongs JK: analyse des tables de vérité, des mécanismes et des applications stratégiques

Cet article explore l'architecture, l'exploitation et diverses applications de la tong-flop JK, à partir de sa structure de base et de ses relations d'entrée-sortie, par le biais d'une mécanique opérationnelle détaillée, à ses implémentations stratégiques dans des systèmes numériques complexes.Le discours s'étend à la distinction entre les variantes déclenchées par le bord et le niveau, analysant leurs utilitaires respectifs dans des environnements synchrones et asynchrones.Catalogue

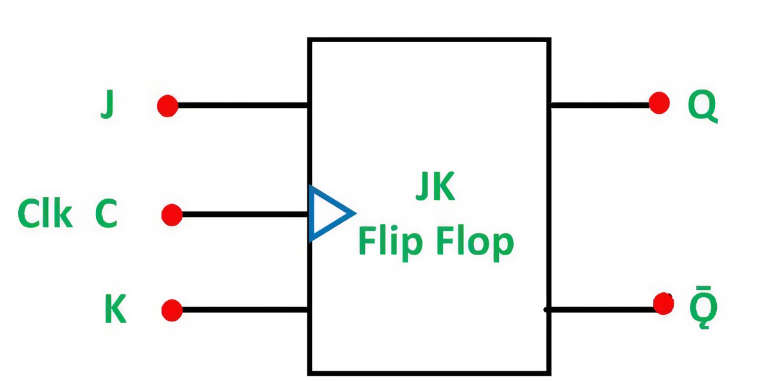

Figure 1: JK Flip-flop

Bases de la bascule JK

Le JK Flip-Flop est un composant de base de l'électronique numérique, conçu pour stocker un seul peu d'informations.Il s'appuie sur la bascule SR plus simple en ajoutant des commentaires, ce qui aide à prévenir les erreurs appelées «conditions de course», où la sortie devient instable.

Cette bascule a deux entrées principales, J (set) et k (réinitialisation), et deux sorties: Q et son complément, q '.Ces sorties reflètent en continu l'état de courant et son opposé, permettant au circuit de s'ajuster et de répondre aux changements d'entrée en temps réel.

Le JK Flip-Flop fonctionne de manière spécifique en fonction des valeurs d'entrée:

• Lorsque J et K sont 0: La tong détient son état actuel.Aucun changement ne se produit.

• Lorsque J et K sont 1: La tong bascule son état.Si q est 0, il devient 1;Si q est 1, il passe à 0. Cette action à bascule est une caractéristique clé qui distingue la bascule JK des conceptions plus simples.

• Lorsque J est 1 et K est 0: La bascule définit son état, ce qui rend Q égal à 1.

• Lorsque J est 0 et K est 1: La tong de bascule réinitialise, ce qui rend Q égal à 0.

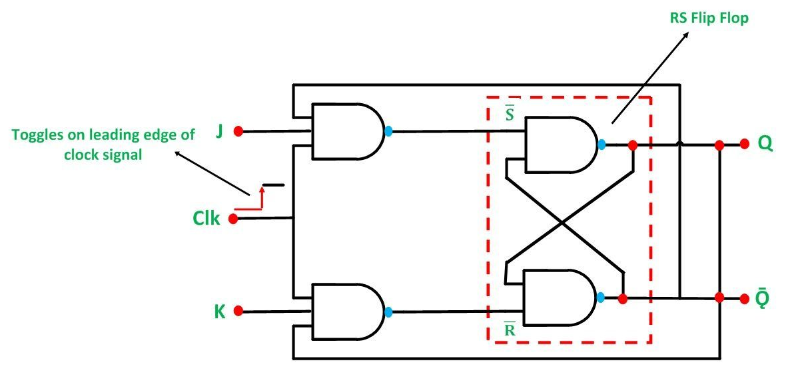

Fonctionnement de la bascule JK

Le JK Flip-Flop joue un rôle clé dans les circuits numériques en gérant la mémoire et le synchronisation grâce à une réponse coordonnée aux signaux d'entrée et aux impulsions d'horloge.Son fonctionnement dépend fortement du moment des entrées J et K par rapport au signal d'horloge, qui détermine comment la sortie indique (Q et Q̅).Cette synchronisation garantit que la bascule se comporte de manière prévisible dans diverses applications de circuit.Le bascule s'appuie sur NAND ou NOR GATES pour gérer ces changements d'état.

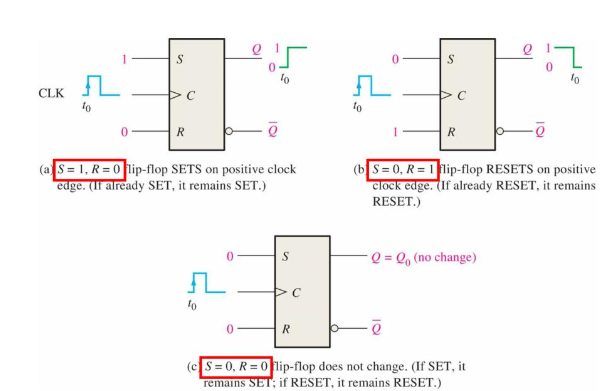

Tenant l'état actuel- Lorsque les entrées J et K sont faibles (0), la bascule maintient son état actuel.Les portes logiques "verrouillent efficacement les sorties, garantissant que l'état précédent (élevé ou bas) est maintenu.Cette fonction de rétention est grave dans les applications où les données doivent rester stables jusqu'à ce qu'un changement spécifique soit indispensable.

Définition de la sortie élevée (État défini) - Lorsque l'impulsion d'horloge se produit et J est élevée (1) tandis que k reste faible (0), les portes logiques s'adaptent pour régler la bascule.Cela entraîne la sortie Q à un état élevé (1).Ceci est utile dans des situations où le circuit doit déclencher une sortie élevée, par exemple, activant un appareil ou stockant un "1" en mémoire.

Effacer la sortie faible (état de réinitialisation) - Si j est faible (0) et k est élevé (1) au moment d'une impulsion d'horloge, la bascule passe à un état de réinitialisation, forçant Q à aller bas (0).Cette action de réinitialisation est souvent utilisée dans les circuits qui ont besoin d'un état par défaut ou effacé après avoir terminé une opération, tel que la compensation des données de la mémoire.

Basculer la sortie - La fonction unique de la bascule émerge lorsque J et K sont élevés (1).Lorsque l'impulsion d'horloge arrive, la bascule bascule, commutant la sortie de son état actuel à celui opposé.Si q est élevé, il devient faible et si q est faible, il devient élevé.Cette fonction de bascule insiste dans des applications telles que des compteurs ou des appareils qui doivent alterner automatiquement entre les états.

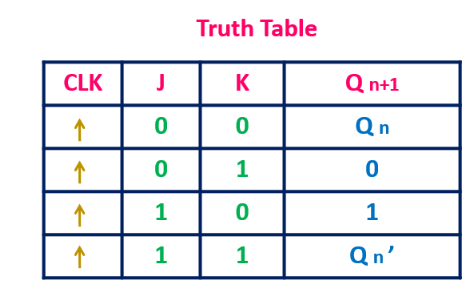

Figure 2: Table de vérité JK Flip-Flop

Analyse de la table de vérité JK Flip-Flop

La table de vérité de la bascule JK est un outil clé pour visualiser la façon dont il réagit aux différents signaux d'entrée en synchronisation avec des impulsions d'horloge.Ce tableau aide à la conception et au dépannage des circuits numériques en montrant comment les sorties de la bascule changent en fonction de diverses conditions d'entrée.

• J et K Low (J = 0, K = 0): Lorsque les deux entrées sont 0, la bascule détient son état actuel.Que Q soit élevé ou bas, il reste inchangé.Ceci est remarquable pour les circuits où la rétention stable des données est recherchée, telles que les éléments en mémoire, où la préservation de l'état actuel convient jusqu'à ce qu'un changement spécifique soit déclenché.

• J High, K Low (J = 1, K = 0): Lorsque J est 1 et K est 0, le bascule définit la sortie Q à High (1).Cette condition de réglage est utile dans les applications qui nécessitent un déclencheur précis pour activer une opération, comme allumer un appareil ou initier une séquence dans un circuit logique.

• J Low, K High (J = 0, K = 1): Avec J à 0 et K à 1, la bascule se réinitialise, ce qui rend Q bas (0).Cette fonction de réinitialisation est grave dans les systèmes qui doivent revenir à un état par défaut, comme lors de la compensation des données ou de l'initialisation d'un processus.

• J et K High (J = 1, K = 1): Lorsque les deux entrées sont élevées, la bascule bascule son état.Si q est élevé, il devient faible et si q est faible, il passe à haut.Ce comportement de bascule est substantiel pour les appareils qui doivent alterner entre les états, comme dans les séparateurs ou compteurs en fréquence.

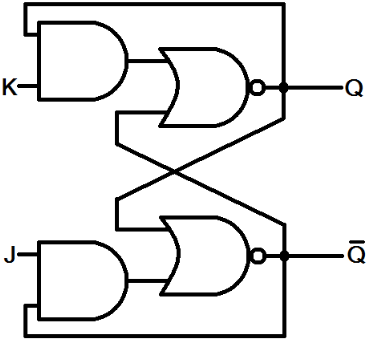

Figure 3: JK Latch

Aperçu de l'exploitation et des utilisations du verrouillage JK

Le verrou JK fonctionne de manière similaire à la bascule JK mais sans avoir besoin d'un signal d'horloge.Au lieu d'attendre un bord d'horloge, le verrou JK répond en continu pour les modifications d'entrée, ce qui la rend «sensible au niveau».Cela signifie que tant que les entrées (J et K) sont stables, la sortie changera en temps réel, offrant une rétroaction immédiate en fonction des conditions d'entrée.

Contrairement à la bascule JK déclenchée par le bord, qui met à jour sa sortie uniquement lorsque le signal d'horloge ne change (de bas à haut ou vice versa), le verrou JK ajuste instantanément sa sortie à mesure que les entrées se déplacent.Cette réactivité constante en temps réel est précieuse dans les scénarios où l'action immédiate est souhaitée sans le retard causé par la synchronisation de l'horloge.

Filtres de bruit: Dans les circuits numériques qui ont besoin de filtrer rapidement le bruit indésirable, la réaction instantanée du verrouillage JK aux modifications d'entrée est influente.Parce qu'il n'attend pas une impulsion d'horloge, il peut ajuster la sortie dès que le bruit est détecté, empêchant les retards dans la correction du signal.

Éléments de mémoire simples: Le verrou JK peut servir d'unité de mémoire de base dans des systèmes qui ne nécessitent pas de contrôle complexe et chronométré.Étant donné que le loquet maintient la sortie stable tant que les entrées ne changent pas, il contient efficacement l'état actuel, ce qui est utile pour les circuits qui doivent conserver des informations sans les frais généraux des opérations chronométrées.

Figure 4: Analyse du diagramme de synchronisation pour la bascule JK

Analyse du diagramme de synchronisation des tongs JK

Un diagramme de synchronisation de la bascule JK fournit une rupture visuelle de la façon dont la sortie répond aux différentes entrées, synchronisées avec les transitions d'impulsion de l'horloge.Ce diagramme montre la relation entre le signal d'horloge (CLK) et les entrées (J et K), et comment elles influencent collectivement les sorties (Q et Q ').Il aide à cartographier le comportement de la bascule à travers les états séquentiels, ce qui facilite la compréhension de son fonctionnement.

Premièrement, le diagramme Souleveillance que les sorties sont mises à jour uniquement sur les bords montant ou descendant de l'impulsion d'horloge.Cette caractéristique, connue sous le nom de déclenchement des bords, est dominante pour le fonctionnement de la bascule JK.Il montre que même si les entrées J et K changent, la sortie reste inchangée jusqu'à ce que le bord d'horloge se produise, garantissant des transitions prévisibles et stables.

Ensuite, comme le diagramme cartose les variations des entrées J et K, il est visuellement démontre comment chaque combinaison d'entrée affecte la sortie. Par exemple, lorsque J et K sont faibles (0), la sortie contient son état de courant.Lorsque j est élevé et que k est faible, la sortie est définie.Cette représentation visuelle claire aide les utilisateurs à comprendre comment la bascule réagit à différentes combinaisons d'entrée en temps réel.

Enfin, Le diagramme de synchronisation montre clairement les transitions entre différents états de sortie, qu'il s'agisse de détenir, de régler, de réinitialiser ou de basculer.Chaque changement d'état est lié directement aux conditions d'entrée et au bord de l'horloge, montrant une relation de cause à effet focale pour la conception et le dépannage des circuits.

Applications polyvalentes des tongs JK

Les bascules JK sont des composants principaux dans un large éventail de systèmes numériques, connu pour leur flexibilité et leur fiabilité.Leur capacité à gérer les opérations logiques complexes les rend nécessaires dans plusieurs applications clés, notamment:

Figure 5: stockage de mémoire

Les bascules JK sont couramment utilisées pour stocker des bits individuels de données, ce qui en fait des éléments fondamentaux dans les réseaux et les registres de mémoire.Chaque bascule contient un bit, garantissant un stockage de données fiable, ce qui est bénéfique dans la conception de systèmes de mémoire plus grands.

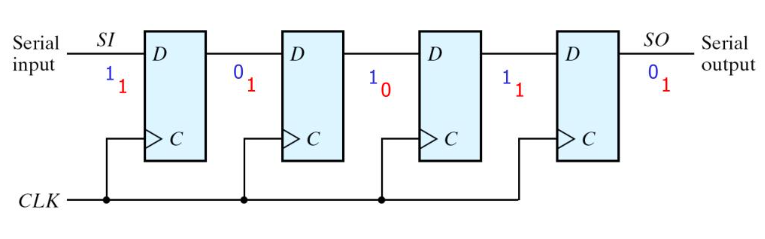

Figure 6: Compteurs et registres de quart

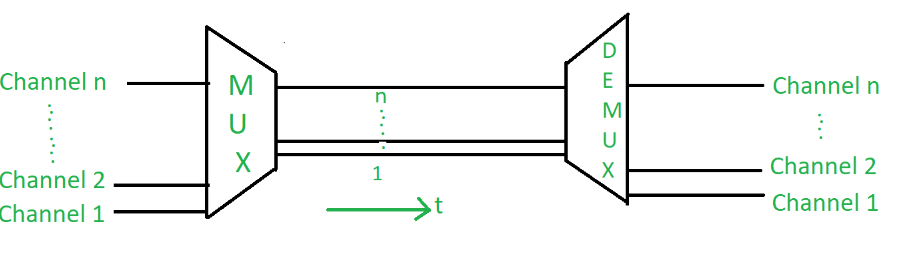

Les bascules JK sont dynamiques dans les opérations de séquençage.Ils sont largement utilisés dans les compteurs pour compter les événements ou les impulsions et dans les registres de décalage pour convertir les données série en formats parallèles.Cela les rend utiles pour gérer et manipuler les données à différentes étapes d'un processus, comme dans les systèmes de communication.

Figure 7: Division de fréquence

Dans le traitement du signal, les bascules JK sont souvent utilisées pour la division de fréquence.En basculant leur état à chaque impulsion d'horloge, ils divisent la fréquence du signal d'entrée, créant un signal d'horloge plus lent et plus gérable.Cela est remarquable dans des applications comme la gestion du signal d'horloge, où le contrôle de synchronisation est souhaité.

Figure 8: Synchronisation

Les bascules JK aident à synchroniser plusieurs processus numériques en veillant à ce que différentes parties d'un système fonctionnent ensemble de manière coordonnée.Ils s'assurent que divers composants répondent correctement aux signaux chronométrés, en gardant l'ensemble du système en synchronisation.

Figure 9: JK Flip-flop: déclenché par le bord et déclenché au niveau

Différents types de bascules JK

Les tongs JK sont disponibles en deux types principaux: déclenché par le bord et déclenché au niveau, chacun conçu pour différentes exigences opérationnelles.

Tongs JK déclenchées par le bord: ne changez pas leur état uniquement à des points spécifiques - lorsque le signal d'horloge passe de faible à haut (bord montant) ou élevé à bas (bord tombant).Cette caractéristique les rend idéales pour les systèmes où un timing précis est insistant.Étant donné que les changements d'état se produisent exactement au bord de l'horloge, ces tongs garantissent que toutes les mises à jour se produisent en synchronisation avec l'impulsion d'horloge.Ce comportement prévisible est dynamique dans des environnements étroitement contrôlés tels que les horloges numériques, les registres et la plupart des circuits séquentiels.Ici, le moment de chaque changement est sérieux pour maintenir la stabilité du système et garantir que les opérations sont synchronisées.

Tongs JK déclenchés au niveau: Fonctionnez différemment, en réagissant au signal d'entrée tant que le signal d'horloge est à un niveau particulier - qu'il soit élevé ou bas.Ils n'attendent pas une transition d'horloge spécifique.Au lieu de cela, tant que l'entrée remplit les conditions requises, la bascule changera les états.Ce comportement rend les tongs déclenchées de niveau mieux adaptés aux systèmes asynchrones, où les entrées peuvent ne pas s'aligner sur une impulsion d'horloge ordinaire.Ils offrent une flexibilité dans les systèmes où les entrées sont imprévisibles ou arrivent à des intervalles irréguliers, comme dans certaines tâches de traitement du signal ou des systèmes de surveillance qui doivent réagir immédiatement aux changements de changement.

Pour les avantages et les inconvénients de JK Flip-Flop

Les bascules JK offrent plusieurs avantages, mais sont également livrés avec des compromis qui doivent être soigneusement pesés lors de la conception de systèmes numériques.

|

Pros |

|

|

Versatilité |

Les bascules JK sont très flexibles et peuvent

être utilisé dans divers circuits numériques comme le stockage de mémoire, les compteurs, et

systèmes de contrôle.Ils peuvent basculer, définir ou réinitialiser en fonction de différentes entrées

conditions, ce qui les rend adaptés à un large éventail d'applications qui

nécessitent un contrôle précis sur les transitions d'état. |

|

Mécanisme d'auto-correction |

L'une des fonctionnalités hors concours de JK

Les tongs sont leur boucle de rétroaction intégrée, ce qui aide à corriger la logique

déclare dynamiquement.Cette auto-correction garantit que le circuit reste

stable pendant le fonctionnement, même lorsque les entrées changent rapidement. |

|

Atténuation des conditions de course |

Contrairement aux tongs plus simples, JK tongs-flops

sont conçus pour empêcher les conditions de course - des situations où la sortie devient

instable en raison de signaux d'entrée contradictoires.Cette capacité à maintenir

La sortie cohérente, même sous des changements d'entrée rapides et séquentiels, améliore le

fiabilité du circuit. |

|

Inconvénients |

|

|

Conception complexe |

Les tongs JK sont plus compliqués que

tongs de base.Leur conception nécessite des portes logiques et des entrées supplémentaires

surveillance, ce qui peut rendre le circuit plus difficile à concevoir et

Dépannage, en particulier dans les systèmes où la simplicité est préférée. |

|

Retard de propagation |

Le déclenchement interne utilisé pour gérer l'État

Les transitions introduisent un retard dans la vitesse de traitement des signaux.Dans

applications à grande vitesse, ce retard peut affecter le calendrier global et ralentir

les performances du circuit. |

|

Consommation d'énergie plus élevée |

En raison de leur complexité et de la nécessité de

Surveillez constamment les conditions d'entrée, les bascules JK consomment plus de puissance

par rapport aux tongs plus simples.Dans des systèmes plus grands ou sensibles à la puissance

applications, cette demande de puissance plus élevée peut devenir un inconvénient |

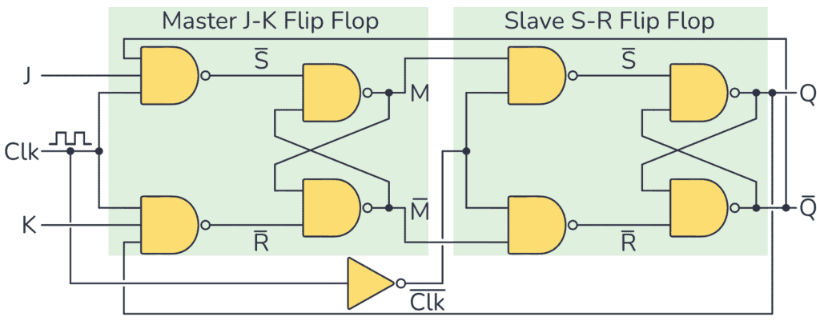

Figure 10: Master-Slave JK Flip-Flop

Décodage de la bascule JK Master-Slave

La bascule JK Master-Slave est conçue pour résoudre l'état de la course de course trouvée dans les bascules JK standard en utilisant un processus en deux étapes pour gérer plus efficacement les entrées et les sorties.

La première étape, appelée étape maître, capture les valeurs d'entrée lorsque le signal d'horloge atteint un bord spécifique, en hausse ou en descendant.À ce stade, les données d'entrée sont verrouillées, ce qui signifie que d'autres modifications des entrées n'affectent pas l'état capturé avant le prochain cycle d'horloge.Cette étape garantit que la bascule enregistre l'entrée correcte sans être influencée par des changements ultérieurs pendant le même cycle d'horloge.

Une fois la scène principale terminée, la scène des esclaves entre en jeu.Cette étape met à jour la sortie en fonction des données capturées par l'étape maître, mais uniquement au bord de l'horloge suivante.En séparant la capture d'entrée de la mise à jour de sortie, l'étape esclave garantit que la sortie reste stable jusqu'à ce que l'étape maître ait complètement traité l'entrée.Cela empêche tout changement prématuré ou involontaire de la sortie pendant le cycle d'horloge.

Pourquoi la configuration maître-esclave est importante?

Le processus en deux étapes stabilise le fonctionnement de la bascule JK, empêchant des oscillations ou des fluctuations indésirables qui peuvent se produire dans des configurations plus simples, en particulier lorsque les deux entrées sont maintenues élevées.En découplant le traitement d'entrée du changement de sortie, la configuration maître-esclave garantit que les sorties restent prévisibles et stables, même dans les situations où le timing est précieux.

Aborder la course autour de l'état dans les tongs JK

Les conditions de race se produisent dans les bascules JK lorsque les deux entrées, J et K, sont élevées et le signal d'horloge reste actif trop longtemps.Cela conduit à une activité continue des sorties, ce qui peut provoquer un comportement erratique et perturber la fiabilité du circuit.

La configuration maître-esclave utilise un processus en deux étapes pour éviter les problèmes de race.L'étape principale capture les valeurs d'entrée au bord de l'horloge et les verrouille. Le stade esclave met à jour les sorties au bord de l'horloge suivante, garantissant que la sortie ne change pas tant que les entrées ne sont pas entièrement traitées.Cette approche empêche efficacement la sortie de basculer de façon incontrôlable, même si les entrées restent élevées pendant une période prolongée.

Une autre méthode pour éviter les conditions de race consiste à ajuster la durée de l'impulsion d'horloge.En rendant l'impulsion d'horloge plus courte que le délai de propagation de la bascule, vous pouvez vous assurer que l'état ne change pas plus d'une fois dans le même cycle d'horloge.Cela empêche la bascule de basculer à plusieurs reprises pendant un seul cycle, stabilisant la sortie.

Dynamique de la commutation dans les tongs JK

Le comportement de commutation d'une bascule JK est largement entraîné par le moment du signal de l'horloge et les niveaux d'entrée (J et K).La bascule modifie l'état basé sur les entrées présentes au bord positif du signal d'horloge.À ce moment dangereux, le bascule évalue les entrées et met à jour sa sortie en conséquence.

Lorsque le signal d'horloge frappe le bord montant, la bascule JK lit les états actuels des entrées J et K.Selon leurs valeurs, la bascule détiendra, définira, réinitialise ou basculera sa sortie.

Horloges numériques: La précision est tout dans les horloges numériques, et JK les tongs Flip aident à maintenir cette précision en garantissant que les changements d'état ne se produisent qu'à des intervalles d'horloge précis.

Testers logiques séquentiels: Dans les systèmes qui testent les fonctionnalités des circuits logiques, JK tongs jouent un rôle dans la vérification que chaque composant répond correctement aux signaux chronométrés spécifiques.

Autres systèmes sensibles au temps: Dans diverses applications numériques où le calendrier est risqué, tel que les systèmes de communication ou les unités de traitement des données, le JK Flip-Flop garantit que les transitions d'état se produisent en synchronisation avec l'horloge, empêchant les erreurs de synchronisation.

Conclusion

Le bascule JK se distingue comme un élément ultime dans la conception du circuit numérique, offrant un mélange de polyvalence et de précision désespérée pour un large éventail d'applications allant du stockage de la mémoire à la division de fréquence et à la synchronisation des processus numériques.Sa capacité à atténuer les conditions de course grâce à des configurations innovantes telles que la disposition des esclaves maître souligne son adaptabilité dans la résolution des défis de conception inhérente.De même, le rôle grave de la bascule de la bascule dans la garantie de transitions d'état précises met en évidence sa nature requise dans la création et la maintenance de systèmes numériques fiables et efficaces.À mesure que la technologie progresse, les conceptions et les applications en évolution de la bascule JK continuent d'être essentielles pour repousser les limites de l'électronique numérique vers des architectures plus sophistiquées et robustes.

Questions fréquemment posées [FAQ]

1. Quelles sont les applications de JK Flip Flop?

La bascule JK est largement utilisée dans l'électronique numérique pour une variété de tâches:

Applications de synchronisation: Il peut servir d'élément de retard ou de minuterie lorsqu'il est connecté dans certaines configurations.

Compteurs et registres: En basculant son état avec chaque impulsion d'horloge, il est utilisé dans la conception de divers compteurs et registres de décalage qui sont ultimes dans les circuits logiques séquentiels.

Stockage de la mémoire: Il fournit une unité de base de stockage de mémoire, utile pour stocker des bits dans les applications de calcul.

2. Comment fonctionne un JK Flip-Flop avec une table de vérité?

Une bascule JK a deux entrées (J et K) et un signal d'horloge.Son fonctionnement varie en fonction des états d'entrée, synchronisés à l'horloge:

• j = 0, k = 0: la sortie ne change pas.

• j = 0, k = 1: la sortie se réinitialise à 0.

• j = 1, k = 0: La sortie est définie sur 1.

• j = 1, k = 1: la sortie bascule (c'est-à-dire si elle était de 0, elle devient 1 et vice versa).

3. Qu'est-ce que JK Flip Flop et fonctionne-t-il?

Une bascule JK combine les propriétés des tongs SR et T.Il évite la condition "interdite" observée dans les bascules SR en utilisant efficacement les entrées JK:

L'état de la bascule est contrôlé par les entrées J et K, qui déterminent si la sortie doit maintenir, réinitialiser, régler ou basculer, en synchronisation avec le bord montant ou en descendant de l'impulsion d'horloge.

4. Quelles sont les applications des verrous et des tongs?

Stockage de données: Les verrous et les tongs sont graves pour le stockage de données dans les registres et les tableaux de mémoire.

Division de fréquence: Utilisé dans les séparateurs de fréquence en raison de leur capacité à changer les états sur les bords de l'horloge, en réalisant de moitié la fréquence à chaque étape d'une série.

Machines d'État: Basique dans la conception de machines d'état finies qui sont utilisées pour implémenter des circuits de logique et de contrôle séquentiels.

Débouning: Utilisé pour stabiliser les signaux des commutateurs et des boutons mécaniques, assurant des transitions uniques et propres.

5. À quoi servent les tongs?

Stockage binaire: Chaque bascule stocke un peu de données, ce qui en fait des blocs de construction pour les dispositifs de stockage binaires.

Diviseurs d'horloge: Ils divisent la fréquence de l'horloge d'entrée par deux, utile dans les horloges numériques et les applications de synchronisation.